USB基础总结

USB 历史

通用串行总线 (USB) 是将外围设备连接到主机的标准接口。USB 系统最初是由康柏、数字设备、IBM、英特尔、微软和北方电信等公司设计的,目的是用更简单的架构取代现有的混合连接器系统。

USB 的设计初衷是取代将外围设备连接到主机所需的大量电缆和连接器。USB 的主要目标是使外围设备的添加变得快速而简单。所有 USB 设备都具有一些共同的关键特性,从而实现这一目标。所有 USB 设备在总线上都可以自我识别。所有设备都可热插拔,以实现真正的即插即用功能。此外,一些设备可以从 USB 获得电力,从而无需额外的电源适配器。

为了确保最大程度的互操作性,USB 标准定义了 USB 系统从物理层(机械和电气)到软件层的所有方面。USB 标准由 USB 实施者论坛 (USB-IF) 维护和执行。USB 设备必须通过 USB-IF 合规性测试,才能被视为合规并能够使用 USB 徽标。

USB 1.0 于 1996 年首次推出,但直到 1998 年 USB 1.1 发布后才得到广泛采用。2000 年,USB 2.0 发布,自此成为将设备连接到计算机及其他设备的事实标准。2008 年,USB 规范扩展为 USB 3.0,也称为超[高速] USB。USB 3.0 代表了 USB 底层操作的重大变化。为了简化用户体验,USB 3.0 被设计为即插即用,并向后兼容 USB 2.0。

USB 3.0 规范包含许多重大变化,其中包括:

- 更高的数据传输速率(高达 5 Gbps)

- 增加总线功率和电流消耗

- 改进电源管理

- 全双工数据通信

- 链路训练和状态机 (LTSSM)

- 中断驱动,而不是轮询

- 流式接口可实现更高效的数据传输

截至 2010 年,USB 标准规定了不同类型的 USB:低速、全速高速和超高速。USB-IF 还发布了其他规范,扩大了 USB 的范围。这些规范包括 On-The-Go (OTG) 和无线 USB。虽然超出了本文档的范围,但可以在 USB-IF 网站上找到有关这些规范的详细信息。

架构概述

USB 是一种主机调度的、基于令牌的串行总线协议。USB 允许在单个 USB 主控制器上连接最多 127 个设备。主机 PC 可以有多个主控制器,这增加了可连接到单台计算机的 USB 设备的最大数量。

设备可以随意连接和断开。主机PC负责根据需要安装和卸载USB设备的驱动程序。

单个 USB 系统由一个 USB 主机和一个或多个 USB 设备组成。系统中还可以有零个或多个 USB 集线器。USB 集线器是一种特殊类型的设备。集线器允许将多个下游设备连接到上游主机或集线器。这样,可以增加物理连接到计算机的设备数量。

USB 设备是连接到主机 PC 的外围设备。USB 设备的功能范围不断增加。设备可以支持一项功能或多项功能。例如,一台多功能打印机通过 USB 连接时可以向主机显示多个设备。它可以显示打印机设备、扫描仪设备、传真设备等。

单个 USB 上的所有设备必须共享总线上可用的带宽。主机 PC 可能有多个总线,每个总线都有自己独立的带宽。大多数情况下,大多数主板上的端口都是成对的,这样每个总线都有两个下游端口。

只能有一个 USB 主机设备。此主机可在单个端口上支持最多 127 个不同的设备。设备层数的上限为 7 层,这意味着最多可以内联连接 5 个集线器。

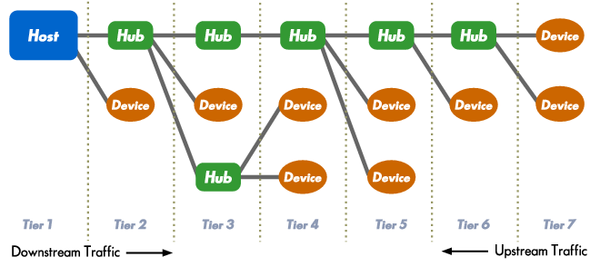

USB 采用分层星型拓扑结构(图 1)。根层是 USB 主机。所有设备都直接或通过集线器连接到主机。根据 USB 规范,USB 主机最多只能支持七层。

USB 2.0 特定架构

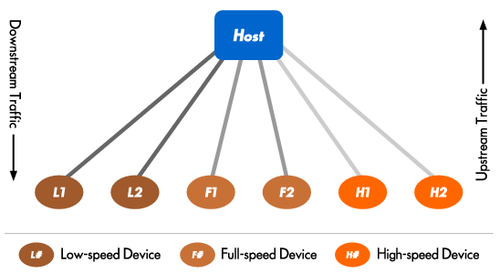

图 2:USB 广播

USB 2.0 主机向其下的所有设备广播信息。低速和高速设备只能看到各自速度的流量。全速设备既能看到自己的速度,也能看到低速流量。

USB 2.0 通过单向广播系统工作。当主机发送数据包时,所有下游设备都会看到该流量。如果主机希望与特定设备通信,则必须在令牌数据包中包含该设备的地址。上游流量(来自设备的响应)仅由主机或直接位于主机返回路径上的集线器看到。

但是,在处理速度不同的设备时,需要注意一些事项。低速和高速设备与其他速度的流量是隔离的。它们只能看到与自己速度相同的流量。参考图 2,这意味着设备 H2 可以看到设备 H1 的下行流量(反之亦然)。此外,设备 L1 的下行流量将被 L2 看到(反之亦然)。但是,全速设备可以使用一种称为低速过全速的特殊信令模式,看到与自己速度相同的流量以及低速流量。这意味着,使用标准全速信令,F2 可以看到 F1 的下行流量(反之亦然),并且 F1 和 F2 也都可以通过特殊的低速过全速信令看到 L1 或 L2 的下行流量。

USB 3.0 特定架构

USB 3.0 标志着现有 USB 基础设施发生了重大变化,几乎影响了所有级别的协议。本文将简要介绍 USB 3.0 的主要功能。有关详细信息,请参阅 USB-IF 的 USB 规范。

USB 3.0 物理接口

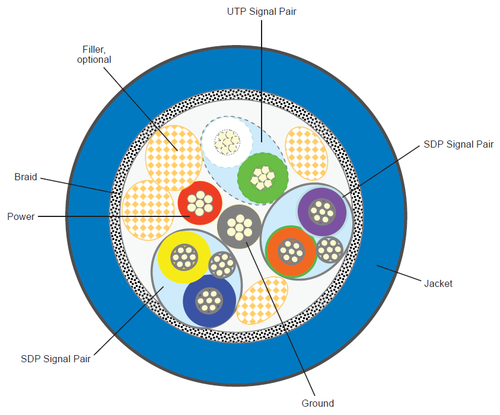

由于 USB 2.0 差分信号的限制,为了能够支持 5 Gbps 数据通信,物理接口进行了升级。除了正常的 USB 2.0 信号外,USB 3.0 电缆和连接器还具有两对额外的差分信号:一对用于发送,一对用于接收,如图 3所示。

图 3:USB 3.0 电缆

USB 3.0 电缆的横截面。图片由 USB Implementers Forum 提供

这两个附加对允许通过 USB 3.0 进行全双工通信。由于原始 USB 2.0 线路保持不变,因此 USB 2.0 通信可以与 USB 3.0 并行进行。

USB 3.0 电源

USB 3.0 的许多关键变化涉及 USB 设备的电源和电源管理。

USB 3.0 电源分配

USB 3.0 增加了 USB 设备可用的电量。对于未配置的设备,可提供 150 mA 的电量,而 USB 2.0 中只有 100 mA 的电量。150 mA 被视为一个单位负载。已配置的设备最多可以吸收 6 个单位负载,即 900 mA,与 USB 2.0 中可用的 500 mA 相比有显著增加。增加的电量允许更多设备通过总线供电。

USB 3.0 电源管理

USB 3.0 提供更好的电源管理设施,以更有效地利用电源并有助于降低总体功耗。

链路级电源管理允许主机或设备启动到较低级别电源状态的转换。共有三种低功耗状态可用,如第 4节所述。

在 USB 3.0 中,不再有定期的设备轮询,并且数据包也不再在总线上广播。现在,在 USB 3.0 中,设备可以在空闲时进入低功耗状态,因为它们不再需要管理这些数据包的接收。

低功耗级别可在设备级别和功能级别配置。设备在空闲时可以暂停全部或部分功能,从而降低功耗。

通过延迟容忍消息传递,设备可以向主机报告其延迟容忍度,从而允许主机系统进入低功耗状态,而不会对总线上的 USB 设备产生负面影响。

USB 3.0 物理层

在 USB 3.0 中,物理层指定了超高速 USB 信号的电气特性——信息如何被扰乱和编码,以及其他层使用的特殊信号序列。

以下是一些特定于 SuperSpeed USB 的新技术的简要概述。

接收器终端

USB 3.0 接收器通过将一个小电阻接地来终止传输线。发送器将检查接收器上的这个终端电阻,以此来检测 USB 3.0 接收器的存在。

数据扰码

物理层使用位扰码来减少线路上的电气干扰问题。但是,发送器可以禁用此功能。

8b/10b 编码

8b/10b 编码将 8 位符号映射到 10 位符号,目的是保持较低的差异,同时继续具有足够的边缘转换以进行时钟恢复。

通过利用 10b 提供的增加的数字空间,可以将差异保持在较低水平。由于所有 8b 值仅占用 10b 数字空间的子集,因此可以使用多个 10b 符号对单个 8b 值进行编码。通常,将使用两个不同的 10b 符号对 8b 值进行编码,其中两个 10b 符号具有不同数量的 1 和 0。选择发送的 10b 符号将最小化线路上现有的差异,目标是实现 1 和 0 的净 50/50 分布。例如,如果一条线路的运行差异为 +2 个 1,则线路上的下一个符号将具有包含更多 0 的位模式。

此外,增加的数字空间允许使用某些控制符号,称为 K 符号,它们不映射到任何 8b 数据值。USB 3.0 将这些控制符号用于多种用途,包括:数据包成帧、弹性缓冲区缓解和数据扰频器控制。

训练序列

为了适应所有制造的发射器、电缆和连接器的各种信号特性,超高速接收器必须在连接到发射器时进行训练。此训练序列有助于配置接收器均衡、极性和数据扰频器,以建立成功的通信链路。

扩频时钟

超高速 USB 在其信号传输中采用扩频时钟。这样做的好处是,扩频时钟不会将所有能量都辐射到高电平的小频带中,而是将其能量分散到稍大的频带中,从而降低任何特定频率的峰值电平。这样做是为了满足 EMC 法规。

低频周期信号 (LFPS)

LFPS 信号是在普通超高速数据线上以较低频率(10-50 MHz 而不是 5 Gbps)发送的边带通信。此边带有助于管理两个端口之间链路上总线上的信号启动和低功耗管理。

弹性缓冲装置

USB 3.0 设备不共享完全相同的时钟源。因此,它们必须能够容忍发射器和接收器上的参考时钟之间的微小差异。为了补偿这种差异,接收器实现了弹性缓冲区,根据收到 SKP 有序集时的缓冲区状态,添加或丢弃“虚拟”数据(称为 SKP 有序集)。

USB 3.0 链路层

链路层负责在主机和设备之间建立和维护可靠的通道。此层有许多关键概念:

链接命令

链路命令用于确保数据包的成功传输、链路流控制和链路电源管理。

链路训练和状态机 (LTSSM)

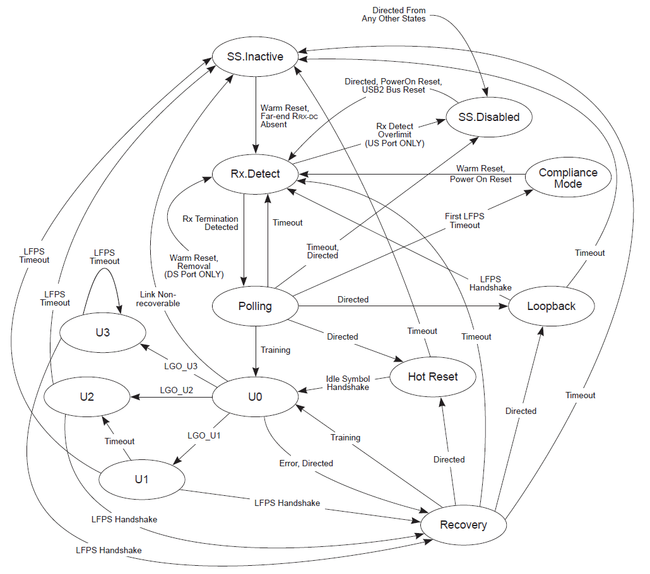

LTSSM 是一个定义链路连接和链路电源管理的状态机。LTSSM 包含 12 种状态:4 种操作链路状态(U0、U1、U2、U3)、4 种链路初始化和训练状态(Rx.Detect、轮询、恢复、热复位)、2 种链路测试状态(环回和合规模式)、SS.Inactive(USB 3.0 无法操作的链路错误状态)和 SS.Disabled(超高速总线被禁用并仅作为 USB 2.0 运行)。图 4列出了 LTSSM 的所有状态,并定义了链路在状态之间的转换方式。

图 4:LTSSM 状态机

链路训练和状态机 (LTSSM) 是 USB 3.0 链路层的核心,定义链路连接和链路电源管理状态和转换。图片由 USB 实施者论坛提供

为了使 USB 3.0 设备进入 U0 操作链路状态,必须对链路进行训练,以便同步主机和设备之间的发射器和接收器。

关键 LTSSM 链接状态:

Rx.检测

这是初始通电状态,其中发送器检查接收器终端是否正确,以确定其超高速伙伴是否存在于总线上。检测到终端后,即可开始链路训练。

轮询

在轮询状态期间,两个链路伙伴训练链路以同步它们的通信,为数据传输做准备。

U0

这是正常运行状态,其中启用超高速信号并且发送和接收 5Gb 数据包。

U1、U2、U3

这些是低功耗状态,其中不传输任何 5Gb 数据包。U1、U2 和 U3 唤醒 U0 的时间越来越长,因此允许发送器进入越来越深的睡眠状态。

USB 3.0 协议层

USB 3.0 协议层管理设备之间的数据流,并指定如何使用不同的数据包结构。

原文转自:https://www.totalphase.com/support/articles/200349256-usb-background

USB百科

USB百科